OPSP Software Manual

RENESAS 32-BIT OPEN PLATFORM SYNTHESIZABLE PROCESSOR

Rev.1.00 Revision date : Mar 01,2004 RenesasTechnology www.renesas.com

### Keep safety first in your circuit designs!

Renesas Technology Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corporation product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corporation or a third party.

- 2. Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination. Any diversion or reexport contrary to the export control laws and regulations of Japan and/ or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.

# **REVISION HISTORY**

# **OPSP** Software Manual

|      |             | Description  |                      |

|------|-------------|--------------|----------------------|

| Rev. | Date        | Page Summary |                      |

| 1.00 | Mar 01,2004 | -            | First edition issued |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

|      |             |              |                      |

This page is blank for reasons of layout.

# Table of contents

### CHAPTER 1 CPU PROGRAMMING MODEL

| 1.1 Processor Modes                                                                |      |

|------------------------------------------------------------------------------------|------|

| 1.1.1 Privileged Instructions                                                      | 1-2  |

| 1.2 CPU Registers                                                                  | 1-2  |

| 1.3 General-purpose Registers                                                      | 1-2  |

| 1.4 Control Registers                                                              | 1-3  |

| 1.4.1 Processor Status Word Register: PSW (CR0)                                    | 1-4  |

| 1.4.2 Condition Bit Register: CBR (CR1)                                            | 1-5  |

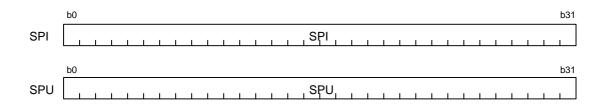

| 1.4.3 Stack Pointer for Interrupt: SPI (CR2) and Stack Pointer for User: SPU (CR3) | 1-5  |

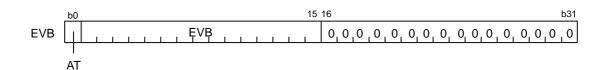

| 1.4.4 EIT Vector Base Register: EVB (CR5)                                          | 1-6  |

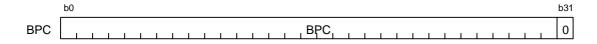

| 1.4.5 Backup PC: BPC (CR6)                                                         | 1-6  |

| 1.5 Accumulators                                                                   | 1-7  |

| 1.6 Program Counter (PC)                                                           | 1-7  |

| 1.7 Data Formats                                                                   | 1-8  |

| 1.7.1 Bi-endian Function                                                           | 1-8  |

| 1.7.2 Data Types                                                                   | 1-8  |

| 1.7.3 Data Formats                                                                 | 1-9  |

| 1.8 Addressing Modes                                                               | 1-11 |

|                                                                                    |      |

### CHAPTER 2 INSTRUCTION SET

| 2.1 Outline of the Instruction Set                      | 2-2  |

|---------------------------------------------------------|------|

| 2.2 Instruction Set                                     | 2-2  |

| 2.2.1 Load and Store Instructions (10 instructions)     | 2-2  |

| 2.2.2 Transfer Instructions (6 instructions)            | 2-4  |

| 2.2.3 Arithmetic/Logical Instructions (46 instructions) | 2-4  |

| 2.2.4 Branch Instructions (21 instructions)             | 2-6  |

| 2.2.5 Bit Manipulating Instructions (5 instructions)    | 2-8  |

| 2.2.6 EIT Related Instructions (2 instructions)         | 2-8  |

| 2.2.7 DSP Function Instructions (22 instructions)       | 2-9  |

| 2.2.8 Coprocessor Support Instructions (3 instructions) | 2-14 |

| 2.3 List of OPSP Extended Instruction Set               | 2-15 |

| 2.3.1 New Extended Instructions of the OPSP-CPU         | 2-15 |

| 2.3.2 Function-Extended Instructions of the OPSP-CPU    | 2-16 |

| 2.4 Instruction Formats                                 | 2-17 |

| 2.5 Parallel Instruction Execution                      | 2-18 |

| 2.5.1 Instruction Formats                               | 2-18 |

| 2.5.2 Parallel Instruction Execution in the OPSP        | 2-19 |

| 2.5.3 16-Bit Instruction List by Category               | 2-19 |

| 2.5.4 Positions of Parallel Executed Instructions       | 2-21 |

| 2.5.5 Operand Interferences                             | 2-22 |

### **CHAPTER 3 INSTRUCTIONS**

| 3.1 Guide to Detailed Instruction Description                         | 3-2   |

|-----------------------------------------------------------------------|-------|

| 3.2 Detailed Description of Instructions                              | 3-6   |

| 3.3 Notes about the BCL and BNCL Instructions                         | 3-127 |

| 3.4 Exception and Trap Handling during Parallel Instruction Execution | 3-128 |

#### APPENDICES

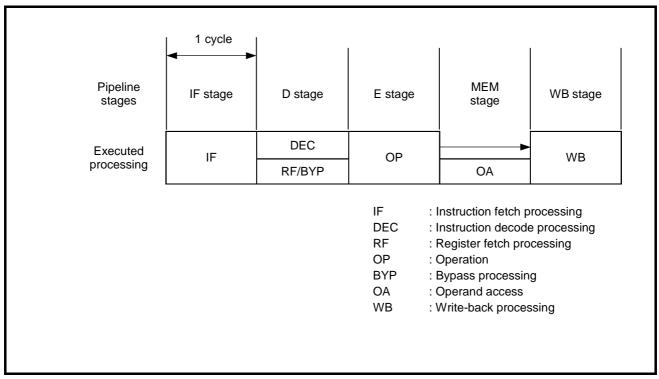

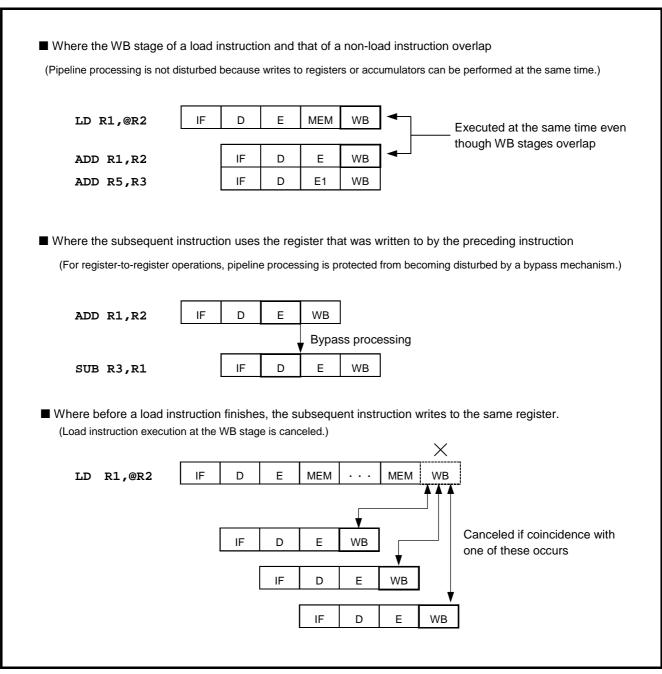

| Appendix 1 Mechanism of Pipelined Instruction Processing         | A-2  |

|------------------------------------------------------------------|------|

| Appendix 1.1 Outline of Pipelined Instruction Processing         | A-2  |

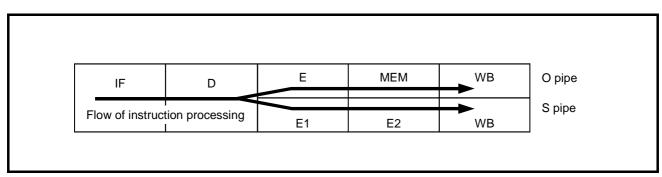

| Appendix 1.2 Flow of Instruction Processing in the O and S Pipes | A-5  |

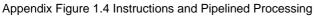

| Appendix 1.3 Instructions and Pipelined Processing               | A-6  |

| Appendix 1.4 Pipelined Processing of Parallel Instructions       | A-7  |

| Appendix 1.5 Basic Pipeline Operation                            | A-8  |

| Appendix 2 Instruction Processing Time                           | A-12 |

CHAPTER 1 CPU PROGRAMMING MODEL

# 1.1 Processor Modes

The OPSP-CPU core (hereafter abbreviated "OPSP-CPU") provides two processor modes: Supervisor Mode and User Mode. A hierarchical resource protection mechanism can be realized by using these processor modes. Each processor mode has designated rights with respect to memory access and executable instructions, which are higher for supervisor mode than for user mode.

When an EIT event occurs, the CPU goes to supervisor mode. The processor mode in which the CPU was immediately before the EIT event occurred is stored in the backup PM (BPM) bit of the Processor Status Word Register (PSW). When the RTE instruction is executed, the CPU returns to the previous processor mode that is stored in the BPM bit.

#### 1.1.1 Privileged Instructions

Privileged instructions are those that can only be executed in supervisor mode. If a privileged instruction is executed in user mode, a privileged instruction exception occurs. The privileged instructions include RTE, MVTC, SETPSW, and CLRPSW.

# 1.2 CPU Registers

The OPSP-CPU has 16 general-purpose registers, 6 control registers, 2 accumulators, and a program counter. The accumulators are configured with 64 bits, while all other registers are configured with 32 bits.

# 1.3 General-purpose Registers

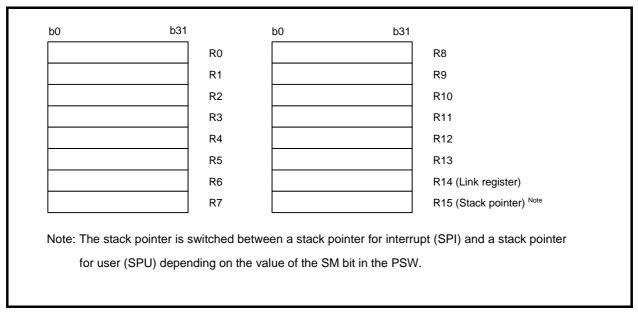

The general-purpose registers are 32 bits wide, and there are 16 of them (R0 to R15). These registers are used to hold data and base addresses. Of these, R14 and R15 are used as a link register and a stack pointer (SPI or SPU), respectively. The link register is used to hold the return address when executing a subroutine call instruction. The stack pointer is switched between a stack pointer for interrupt (SPI) and a stack pointer for user (SPU) depending on the value of the stack mode (SM) bit in the Processor Status Word Register (PSW).

Figure 1.3.1 General-purpose Registers

# **1.4 Control Registers**

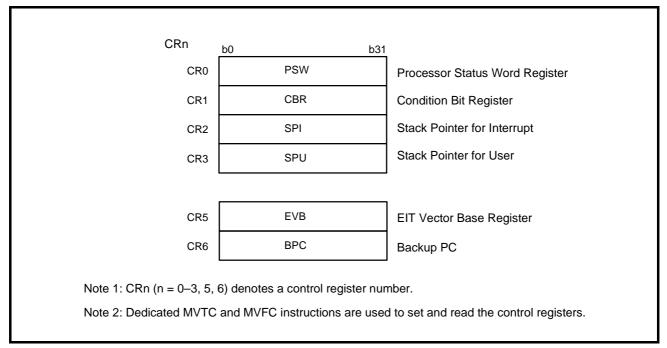

There are six control registers: Processor Status Word Register (PSW), Condition Bit Register (C), Stack Pointer for Interrupt (SPI), Stack Pointer for User (SPU), EIT Vector Base Register (EVB), and Backup PC (BPC).

Dedicated MVTC and MVFC instructions are used to set and read these control registers. Furthermore, SETPSW and CLRPSW instructions can be used for the PSW.

MVTC, SETPSW, and CLRPSW are the privileged instructions that can only be executed when the CPU is operating in supervisor mode. Which processor mode is active is determined by the processor mode (PM) bit in the Processor Status Word Register (PSW).

Figure 1.4.1 Control Registers

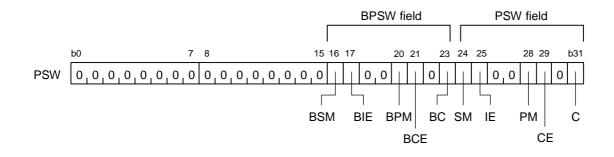

#### 1.4.1 Processor Status Word Register: PSW (CR0)

The Processor Status Word Register (PSW) indicates the status of the OPSP-CPU. It consists of two bit fields: the PSW field that is normally used, and the BPSW field in which the PSW field is saved when an EIT occurs.

The PSW field further consists of the stack mode bit (SM), interrupt enable bit (IE), processor mode bit (PM), coprocessor interrupt enable bit (CE), and condition bit (C). Similarly, the BPSW field consists of the backup SM bit (BSM), backup IE bit (BIE), backup PM bit (BPM), backup CE bit (BCE), and backup C bit (BC).

After reset, the BSM, BIE, BPM, BCE, and BC are indeterminate. All other bits are 0.

To switch the processor mode, set BPM = 1 using the MVTC instruction and then execute the RTE instruction to branch to the user space(H'0000 0000 – H'7FFF FFFF). If the PM bit needs to be altered directly with the MVTC instruction, always be sure to alter it in the user space.

| b     | Bit Name                                    | Function                                              | R | W |

|-------|---------------------------------------------|-------------------------------------------------------|---|---|

| 0–15  | No functions assigned. Fix these bits to 0. |                                                       | 0 | 0 |

| 16    | BSM                                         | Save the value of the SM bit when an EIT is accepted. | R | W |

|       | Backup SM bit                               |                                                       |   |   |

| 17    | BIE                                         | Save the value of the IE bit when an EIT is accepted. | R | W |

|       | Backup IE bit                               |                                                       |   |   |

| 18–19 | No functions assigned. Fix these            | bits to 0.                                            | 0 | 0 |

| 20    | BPM                                         | Save the value of the PM bit when an EIT is accepted. | R | W |

|       | Backup PM bit                               |                                                       |   |   |

| 21    | BCE                                         | Save the value of the CE bit when an EIT is accepted. | R | W |

|       | Backup CE bit                               |                                                       |   |   |

| 22    | No functions assigned. Fix these            | bits to 0.                                            | 0 | 0 |

| 23    | BC                                          | Save the value of the C bit when an EIT is accepted.  | R | W |

|       | Backup C bit                                |                                                       |   |   |

| 24    | SM                                          | 0: Stack pointer for interrupt is used.               | R | W |

|       | Stack mode bit                              | 1: Stack pointer for user is used.                    |   |   |

| 25    | IE                                          | 0: Interrupt acceptance disabled                      | R | W |

|       | Interrupt enable bit                        | 1: Interrupt acceptance enabled                       |   |   |

| 26–27 | No functions assigned. Fix these            | bits to 0.                                            | 0 | 0 |

| 28    | PM                                          | 0: Supervisor mode                                    | R | W |

|       | Processor mode bit                          | 1: User mode                                          |   |   |

| 29    | CE                                          | 0: Coprocessor interrupt not accepted                 | R | W |

|       | Coprocessor interrupt enable bit            | 1: Coprocessor interrupt accepted                     |   |   |

| 30 | No functions assigned. Fix these bits to 0. |                                                                        | 0 | 0 |

|----|---------------------------------------------|------------------------------------------------------------------------|---|---|

| 31 | С                                           | Indicate whether instruction execution resulted in a carry, borrow, or | R | W |

|    | Condition bit                               | overflow.                                                              |   |   |

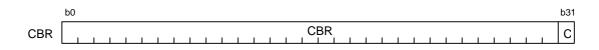

#### 1.4.2 Condition Bit Register: CBR (CR1)

The Condition Bit Register (CBR) is derived from the condition bit (C) of the PSW to serve as a separate register. The value written to the condition bit in the PSW is reflected in this register. This register can only be read. (Writing to this register with the MVTC instruction is ignored.)

After reset, the CBR is H'0000 0000.

#### 1.4.3 Stack Pointer for Interrupt: SPI (CR2) and Stack Pointer for User: SPU (CR3)

The Stack Pointer for Interrupt (SPI) and the Stack Pointer for User (SPU) hold the address of the current stack pointer. These registers can be accessed as the general-purpose register R15. Whether R15 is used as the SPI or as the SPU is determined by the stack mode bit (SM) in the PSW.

#### 1.4.4 EIT Vector Base Register: EVB (CR5)

The EIT Vector Base Register (EVB) holds the EIT vector entry start address. The 16 high-order bits of the EIT vector entry start address comprise the value of the 16 high-order bits in this register.

<After reset: H'0000 0000>

| b     | Bit Name                                    | Function                                      | R | W |

|-------|---------------------------------------------|-----------------------------------------------|---|---|

| 0     | AT                                          | Address translation mode                      | R | Ν |

|       | Address translation mode bit                |                                               |   |   |

| 1–15  | EVB                                         | Set A1–A15 of EIT vector entry in these bits. | R | W |

|       | Vector base bit                             |                                               |   |   |

| 16–31 | No functions assigned. Fix these bits to 0. |                                               | 0 | 0 |

#### (1) AT (address translation mode) bit (b0)

This bit is a copy of the address translation mode bit (AT) in the MATM register, and is a read-only bit.

#### (2) EVB (EIT vector base) bits (b1-b15)

These bits set the EIT vector entry start address A1–A15. However, the reset interrupt (RI) vector is located at the address H'0000 0000 no matter how the EIT vector base bits are set.

Note: The EVB register can be set only once immediately after reset. Write to the EVB register should be performed at the beginning of a reset handler.

#### 1.4.5 Backup PC: BPC (CR6)

The Backup PC (BPC) is used to save the value of the program counter (PC) when an EIT occurs. Bit 31 is fixed to 0.

When an EIT occurs, the PC value at which the EIT occurred or the PC value for the next instruction is set in the BPC depending on the type of the EIT that occurred. The value of the BPC is returned to the PC when the RTE instruction is executed.

# **1.5 Accumulators**

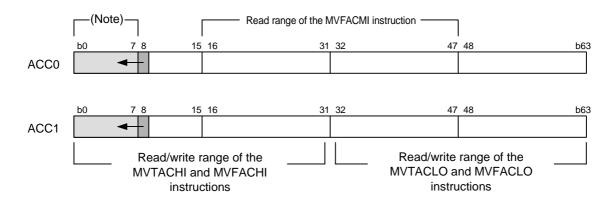

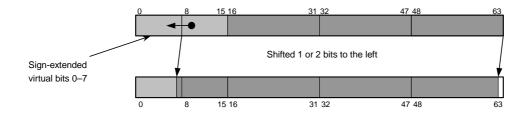

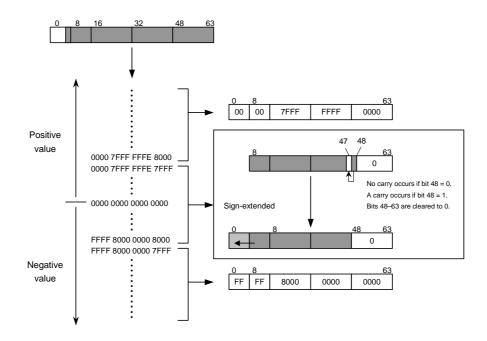

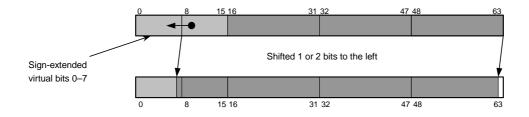

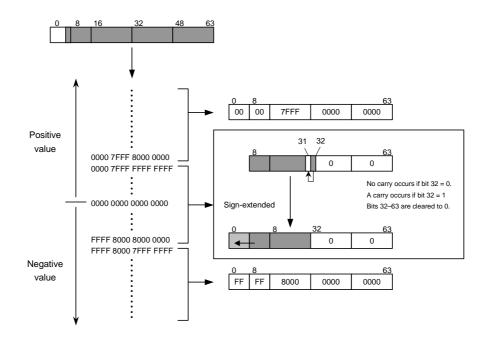

The accumulator is a 56-bit register used in the instructions for the DSP function. There are two of such accumulators, ACC0 and ACC1. During read or write, the accumulator is handled as a 64-bit register. In this case, bits 0–7 in the accumulator are sign-extended with the value of bit 8 during read, and are ignored during write. The accumulator is also used in the multiplication instruction "MUL." Be aware that when this instruction is executed, the value of the accumulator, whether ACC0 or ACC1, is destroyed.

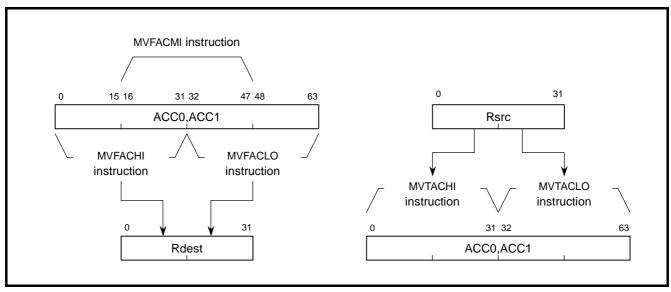

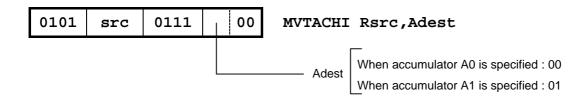

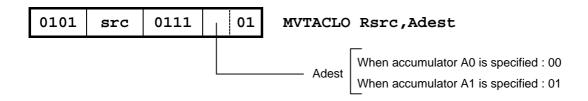

Use the MVTACHI and MVTACLO instructions to write to the accumulator. The MVTACHI and MVTACLO instructions write data to the 32 high-order bits (bits 0–31) and the 32 low-order bits (bits 32–63) in the accumulator, respectively.

Use the MVFACHI, MVFACLO, and MVFACMI instructions to read the accumulator. The MVFACHI, MVFACLO, and MVFACMI instructions read data from the 32 high-order bits (bits 0–31), the 32 low-order bits (bits 32–63), and the 32 middle bits (bits 16–47) in the accumulator, respectively.

After reset, ACC0 and ACC1 are indeterminate.

Note: Bits 0–7 when read always show the value that is sign-extended with the value of bit 8. Write to this bit field is ignored.

### 1.6 Program Counter (PC)

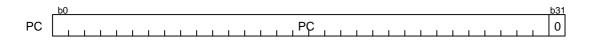

The Program Counter (PC) is a 32-bit counter that holds the address of the currently executed instruction. Since the instructions in the OPSP-CPU begin from even addresses, the LSB (bit 31) in the PC is always 0. After reset, the PC is H'0000 0000.

# 1.7 Data Formats

### 1.7.1 Bi-endian Function

The OPSP-CPU supports the bi-endian function that allows either data format, big endian or little endian, to be adopted.

This manual is written for operation in big endian mode.

### 1.7.2 Data Types

The data types that the instruction set of the OPSP-CPU can handle are signed or unsigned 8, 16, and 32-bit integers. Signed integer values are represented by the 2's complement.

| Signed byte (8-bit) integer        | b0 b7       |     |          |     |

|------------------------------------|-------------|-----|----------|-----|

| Unsigned byte<br>(8-bit) integer   | b0 b7       |     |          |     |

| Signed halfword (16-bit) integer   | b0<br>S     | b15 |          |     |

| Unsigned halfword (16-bit) integer | b0          | b15 |          |     |

| Signed word (32-bit) integer       | b0<br>S     |     | <u> </u> | b31 |

| Unsigned word (32-bit) integer     | b0          |     | I        | b31 |

|                                    | S: Sign bit |     |          |     |

Figure 1.7.1 Data Types

### 1.7.3 Data Formats

#### (1) Data formats in the OPSP-CPU registers

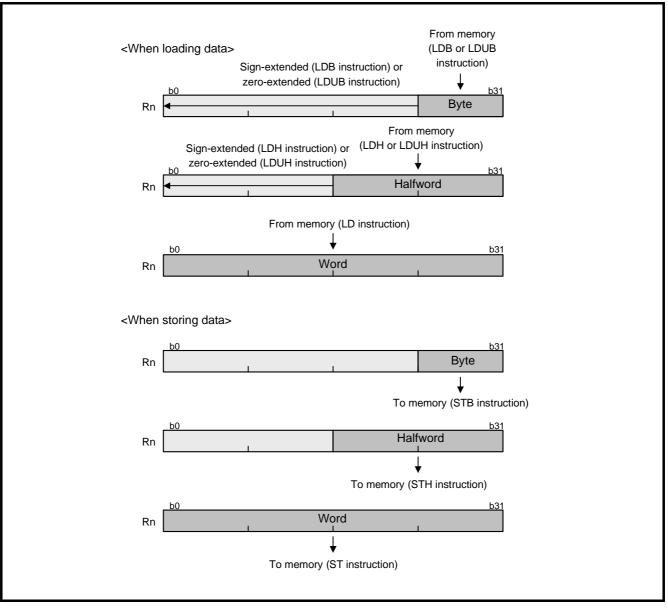

The data size in the OPSP-CPU registers is always the word (32 bits). When byte (8-bit) or halfword (16-bit) data in memory is loaded into a register, the data is sign-extended (LDB, LDH instructions) or zero-extended (LDUB, LDUH instructions) to the word (32-bit) quantity before being stored in the register.

When data in an OPSP-CPU register is stored into memory, the ST, STH, or STB instruction is used. The ST, STH, and STB instructions store the full 32-bit data, the lower 16-bit data, or the least significant 8-bit data of the register in memory, respectively.

Figure 1.7.2 Data Formats in Registers

#### (2) Data formats in memory

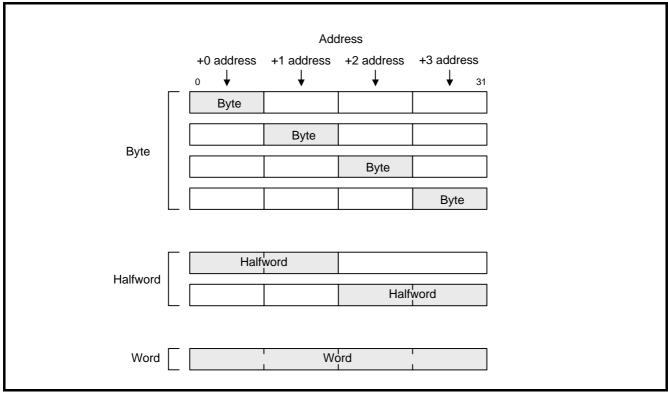

The data in memory has one of three data sizes: byte (8 bits), halfword (16 bits), or word (32 bits). Although byte data can be located at any address, halfword and word data must be located at halfword-aligned addresses (least significant address bit = 0) and word-aligned addresses (two least significant address bits = 00), respectively. If access to misaligned memory data is attempted, an address exception occurs.

Figure 1.7.3 Data Formats in Memory

1.8 Addressing Modes

# **1.8 Addressing Modes**

The OPSP-CPU has the following addressing modes:

(1) Register direct [expressed as R or CR or A<sup>Note</sup>]

A general-purpose or control register or an accumulator is specified directly as the target to be operated on.

#### (2) Register indirect [expressed as @R]

The address is indicated indirectly by a register value. (This addressing mode can be specified in all load and store instructions.)

#### (3) Register relative indirect (expressed as @(disp,R)]

The address is indicated indirectly by (register value) + (16-bit displacement which is sign-extended to 32 bits).

#### (4) Register indirect + register update

- Register value incremented by 1

- The address is indicated by a preupdate register value (specifiable in only STB instruction)

- Register value incremented by 2 The address is indicated by a preupdate register value (specifiable in only STH instruction)

- Register value incremented by 4

The address is indicated by a preupdate register value (specifiable in only LD instruction)

- Register value incremented by 4 The address is indicated by an updated register value (specifiable in only ST instruction)

- Register value decremented by 4

The address is indicated by an updated register value (specifiable in only ST instruction)

#### (5) Immediate [expressed as #imm]

1, 4, 5, 8, 16, or 24-bit immediate value. (For details on how the value is handled, refer to the detailed description of each instruction in the latter part of this manual.)

#### (6) PC relative [expressed as pcdisp]

The address is indicated by (PC value) + (8, 16, or 24-bit displacement which is sign-extended to 32 bits and then shifted left 2 bits).

Note: The accumulators ACC0 and ACC1 are mnemonically expressed as A0 and A1, respectively.

This page is blank for reasons of layout.

# CHAPTER 2 INSTRUCTION SET

# 2.1 Outline of the Instruction Set

The OPSP-CPU has 115 distinct instructions. A RISC architecture is adopted for the OPSP-CPU, so that memory access basically is accomplished by using load and store instructions. Arithmetic/logical operations are executed by register-to-register operation. Furthermore, compound instructions such as Load & Address Update and Store & Address Update are supported.

# 2.2 Instruction Set

The instruction set of the OPSP-CPU is shown below.

New instructions that have been added in the OPSP-CPU from the M32R family instruction set are marked by double asterisks (\*\*), and function-extended instructions are marked by a single asterisk (\*).

### 2.2.1 Load and Store Instructions (10 instructions)

These instructions perform data transfer between memory and a register.

| LD     | Load                   |

|--------|------------------------|

| LDB    | Load byte              |

| LDUB   | Load unsigned byte     |

| LDH    | Load halfword          |

| LDUH   | Load unsigned halfword |

| LOCK   | Load locked            |

| ST     | Store                  |

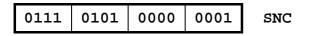

| STB    | Store byte             |

| STH    | Store halfword         |

| UNLOCK | Store unlocked         |

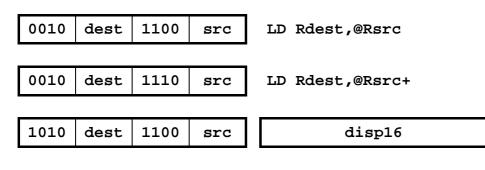

Following three addressing modes can be specified in the load and store instructions.

(1) Register indirect

The address is indicated indirectly by a register value. (This addressing mode can be specified in all load and store instructions.)

(2) Register relative indirect

The address is indicated indirectly by (register value) + (16-bit displacement which is sign-extended to 32 bits). (This addressing mode can be specified in all load and store instructions other than LOCK and UNLOCK.)

(3) Register indirect + register update

- Register value incremented by 1

- The address is indicated by a preupdate register value (specifiable in only STB instruction)

- Register value incremented by 2 The address is indicated by a preupdate register value (specifiable in only STH instruction)

Register value incremented by 4

- The address is indicated by a preupdate register value (specifiable in only LD instruction)

- Register value incremented by 4 The address is indicated by an updated register value (specifiable in only ST instruction)

- Register value decremented by 4

- The address is indicated by an updated register value (specifiable in only ST instruction)

Whichever addressing mode is used, rules for the data formats in memory must be observed. To access halfword or word data, a halfword aligned or word aligned address must be specified, respectively. (The two least significant bits of the accessed address must be "00" or "10" for halfword data, or "00" for word data.) If a misaligned address is specified, an address exception occurs.

If byte or halfword data is accessed in a load instruction, the data has its high order bits sign or zero-extended to become 32-bit data before being stored in a register.

### 2.2.2 Transfer Instructions (6 instructions)

These instructions perform a register to register transfer or a register to immediate transfer.

| LD24 | Load 24-bit immediate      |

|------|----------------------------|

| LDI  | Load immediate             |

| MV   | Move register              |

| MVFC | Move form control register |

| MVTC | Move to control register   |

| SETH | Set high-order 16bit       |

#### 2.2.3 Arithmetic/Logical Instructions (46 instructions)

These instructions perform register to register comparison, arithmetic/logical operation, multiplication/division, or shift operation.

Comparison (7 instructions)

|    | CMP    | Compare                       |

|----|--------|-------------------------------|

| ** | CMPEQ  | Compare equal to              |

|    | CMPI   | Compare immediate             |

|    | CMPU   | Compare unsigned              |

|    | CMPUI  | Compare unsigned immediate    |

| ** | CMPZ   | Compare equal to zero         |

| ** | PCMPBZ | Parallel compare byte to zero |

#### ■ Arithmetic operation (10 instructions)

| ADD   | Add                         |

|-------|-----------------------------|

| ADD3  | Add 3-operand               |

| ADDI  | Add immediate               |

| ADDV  | Add with overflow           |

| ADDV3 | Add 3-operand with overflow |

| ADDX  | Add with carry              |

| NEG   | Negate                      |

| SUB   | Subtract                    |

| SUBV  | Subtract with over flow     |

| SUBX  | Subtract with borrow        |

|       |                             |

#### ■ Logical operation (7 instructions)

| AND  | AND                    |

|------|------------------------|

| AND3 | AND 3-operand          |

| NOT  | Logical NOT            |

| OR   | OR                     |

| OR3  | OR 3-operand           |

| XOR  | Exclusive OR           |

| XOR3 | Exclusive OR 3-operand |

Multiplication/division (13 instructions)

|    | •     | ,                          |

|----|-------|----------------------------|

|    | DIV   | Divide                     |

| ** | DIVB  | Divide byte                |

| ** | DIVH  | Divide halfword            |

|    | DIVU  | Divide unsigned            |

| ** | DIVUB | Divide unsigned byte       |

| ** | DIVUH | Divide unsigned halfword   |

|    | MUL   | Multiply                   |

|    | REM   | Reminder                   |

| ** | REMB  | Reminder byte              |

| ** | REMH  | Reminder halfword          |

|    | REMU  | Reminder unsigned          |

| ** | REMUB | Reminder unsigned byte     |

| ** | REMUH | Reminder unsigned halfword |

|    |       |                            |

■ Shift (9 instructions)

| SLL  | Shift left logical               |

|------|----------------------------------|

| SLL3 | Shift left logical 3-operand     |

| SLLI | Shift left logical immediate     |

| SRA  | Shift right arithmetic           |

| SRA3 | Shift right arithmetic 3-operand |

| SRAI | Shift right arithmetic immediate |

| SRL  | Shift right logical              |

| SRL3 | Shift right logical 3-operand    |

| SRLI | Shift right logical immediate    |

|      |                                  |

#### 2.2.4 Branch Instructions (21 instructions)

These instructions are used to change the program flow.

|    | BC   | Branch on C-bit                         |

|----|------|-----------------------------------------|

| ** | BCL  | Branch and link on C-bit                |

|    | BEQ  | Branch on equal to                      |

|    | BEQZ | Branch on equal to zero                 |

|    | BGEZ | Branch on greater than or equal to zero |

|    | BGTZ | Branch on greater than zero             |

|    | BL   | Branch and link                         |

|    | BLEZ | Branch on less than or equal to zero    |

|    | BLTZ | Branch on less than zero                |

|    | BNC  | Branch on not C-bit                     |

| ** | BNCL | Branch and link on not C-bit            |

|    | BNE  | Branch on not equal to                  |

|    | BNEZ | Branch on not equal to zero             |

|    | BRA  | Branch                                  |

| ** | JC   | Jump on C-bit                           |

|    | JL   | Jump and link                           |

|    | JMP  | Jump                                    |

| ** | JNC  | Jump on not C-bit                       |

|    | NOP  | No operation                            |

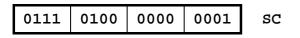

| ** | SC   | Skip on C-bit                           |

| ** | SNC  | Skip on not C-bit                       |

Only the word aligned addresses (those aligned with word boundaries) can be specified as the jump address.

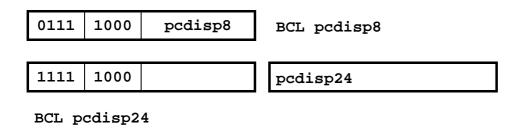

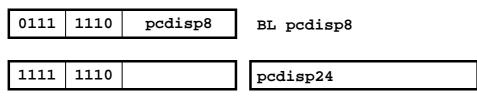

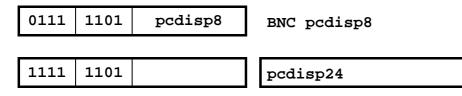

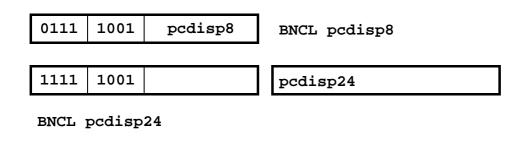

For the BRA, BL, BC, BNC, BCL and BNCL instructions, an 8-bit or 24-bit immediate value can be specified in addressing mode. For the BEQ, BNE, BEQZ, BNEZ, BGTZ, BLTZ, BGEZ and BLEZ instructions, a 16-bit immediate value should be specified in addressing mode.

For the JMP, JL, JC and JNC instructions, the jump address is specified by a register value. However, the two least significant address bits are ignored.

For the SC and SNC instructions, the jump address is indicated by (PC value of the branch instruction) + 4.

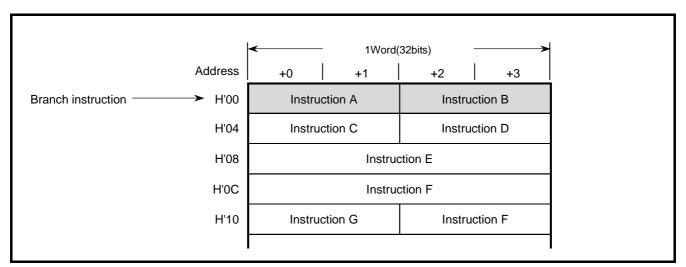

For other branch instructions, the jump address is indicated by (PC value of branch instruction) + (sign-extended immediate value that is shifted two bits left). However, the two least significant bits of the PC value are cleared to 0 when an addition is performed. In Figure 2.2.1, for example, assume that instruction A or instruction B is the branch instruction, and that the program is to jump to instruction G. Then the immediate value, in either case, is 4.

For the JL, BL, BCL and BNCL instructions that are used for subroutine calls, the PC value for the return address is stored in R14 at the same time the program branches off. The value stored in R14 is (PC value of branch instruction + 4), with the two least significant bits of the PC value cleared to 0. In Figure2.2.1, for example, assume that instruction A or instruction B is the JL, BL, BCL, or BNCL instruction. Then the return address, in either case, is the "instruction C."

Figure 2.2.1 Jump Address of a Branch Instruction

#### 2.2.5 Bit Manipulating Instructions (5 instructions)

These instructions set or clear the bits in memory or registers and those in the Processor Status Word Register (PSW).

| ** | BCLR   | Bit clear |

|----|--------|-----------|

| ** | BSET   | Bit set   |

| ** | BTST   | Bit test  |

| ** | CLRPSW | Clear PSW |

| ** | SETPSW | Set PSW   |

|    |        |           |

#### 2.2.6 EIT Related Instructions (2 instructions)

These instructions are provided for EIT events (Exception, Interrupt and Trap). These include an instruction to invoke a trap and an instruction to return from EIT handling.

- \* TRAP Trap

- \* RTE Return from EIT

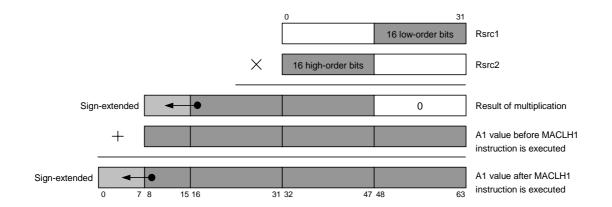

#### 2.2.7 DSP Function Instructions (22 instructions)

In the OPSP-CPU, the DPS function instructions of the M32R family instruction set have been extended as follows:

- There are two accumulators, compared to one in the past.

- Multiply-accumulate operations are enhanced.

- New general-purpose register rounding instructions are added.

The DPS function instructions of the OPSP-CPU are shown below.

New instructions that have been added in the OPSP-CPU from the M32R family instruction set are marked by double asterisks (\*\*), and function-extended instructions are marked by a single asterisk (\*).

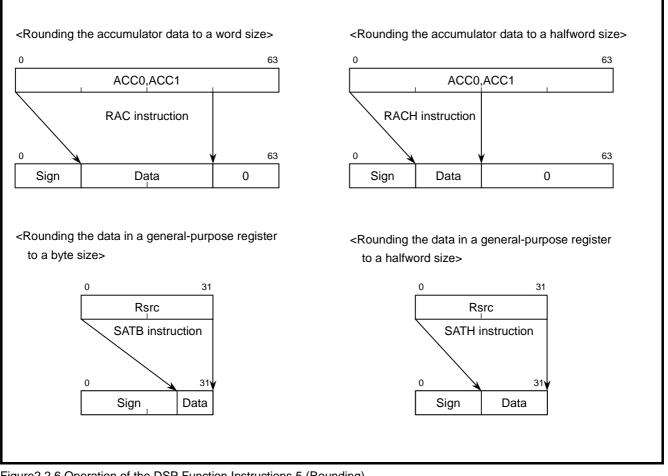

These instructions include those that perform 32 bit  $\times$  16 bit or 16 bit  $\times$  16 bit multiply or multiply-accumulate operations. Also included are those that round the data in an accumulator or general-purpose register or perform data transfer between an accumulator and general-purpose register.

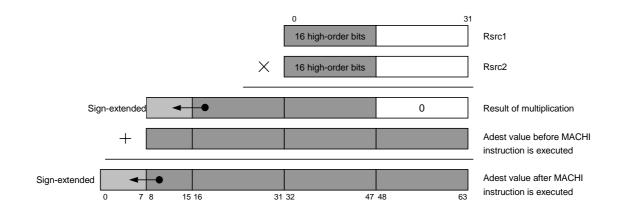

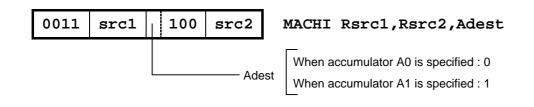

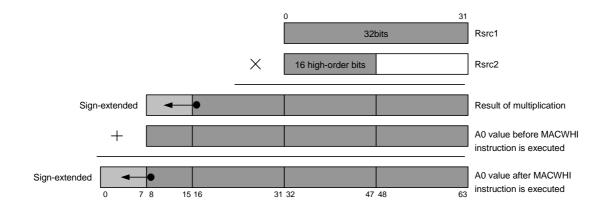

| *  | MACHI   | Multiply-accumulate high-order halfwords                             |

|----|---------|----------------------------------------------------------------------|

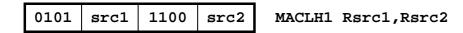

| ** | MACLH1  | Multiply-accumulate low-order halfword and high-order halfword using |

|    |         | accumulator1                                                         |

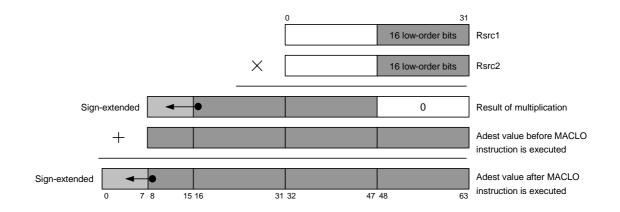

| *  | MACLO   | Multiply-accumulate low-order halfwords                              |

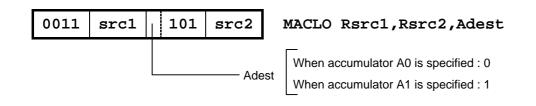

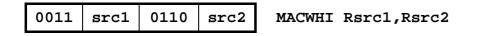

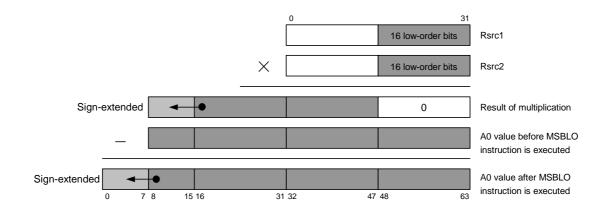

|    | MACWHI  | Multiply-accumulate word and high-order halfword                     |

|    | MACWLO  | Multiply-accumulate word and low-order halfword                      |

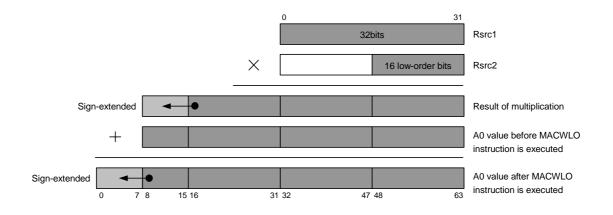

| ** | MACWU1  | Multiply-accumulate word and unsigned low-order halfword using       |

|    |         | accumulator1                                                         |

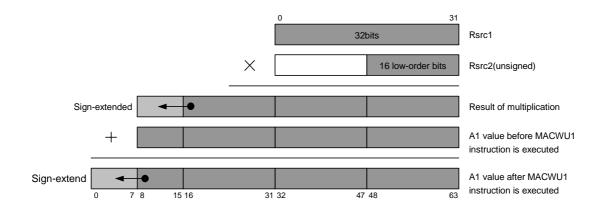

| ** | MSBLO   | Multiply low-order halfwords and subtract                            |

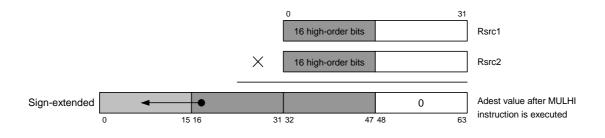

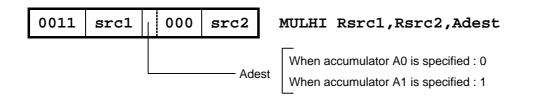

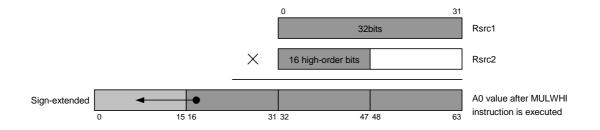

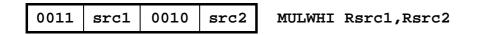

| *  | MULHI   | Multiply high-order halfwords                                        |

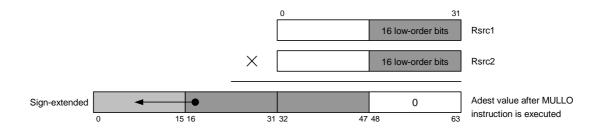

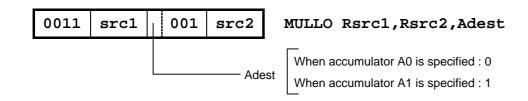

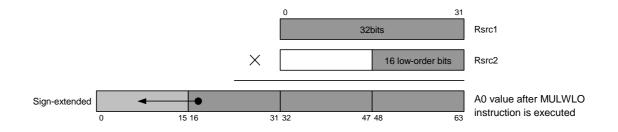

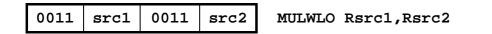

| *  | MULLO   | Multiply low-order halfwords                                         |

|    | MULWHI  | Multiply word and high-order halfword                                |

|    | MULWLO  | Multiply word and low-order halfword                                 |

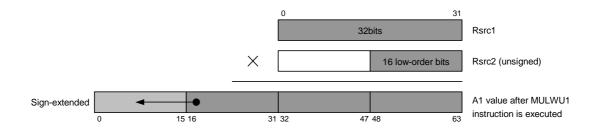

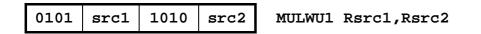

| ** | MULWU1  | Multiply word and unsigned low-order halfword                        |

|    |         | using accumulator1                                                   |

| *  | MVFACHI | Move high-order word from accumulator                                |

| *  | MVFACLO | Move low-order word from accumulator                                 |

| *  | MVFACMI | Move middle-order word from accumulator                              |

| *  | MVTACHI | Move high-order word to accumulator                                  |

| *  | MVTACLO | Move low-order word to accumulator                                   |

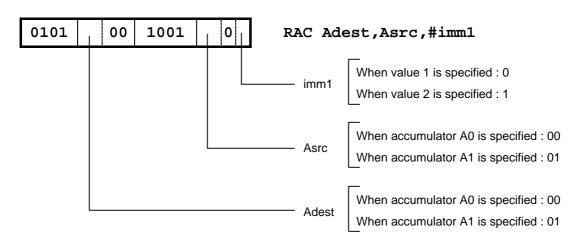

| *  | RAC     | Round accumulator                                                    |

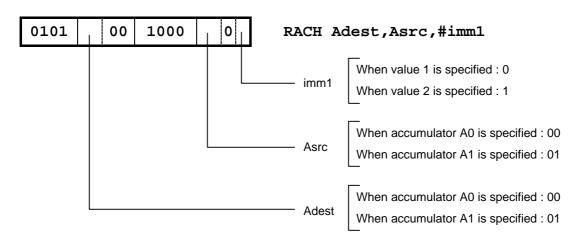

| *  | RACH    | Round accumulator halfword                                           |

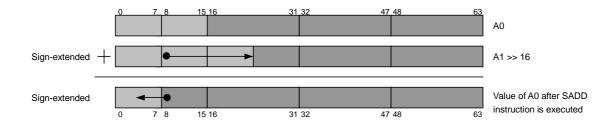

| ** | SADD    | Add accumulators                                                     |

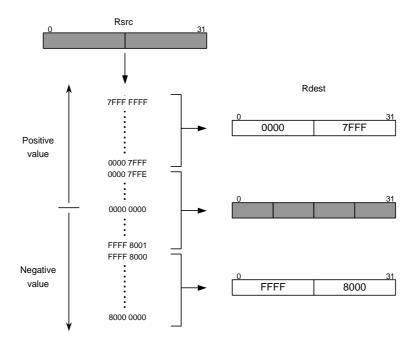

| ** | SATB    | Saturate word into byte                                              |

| ** | SATH    | Saturate word into halfword                                          |

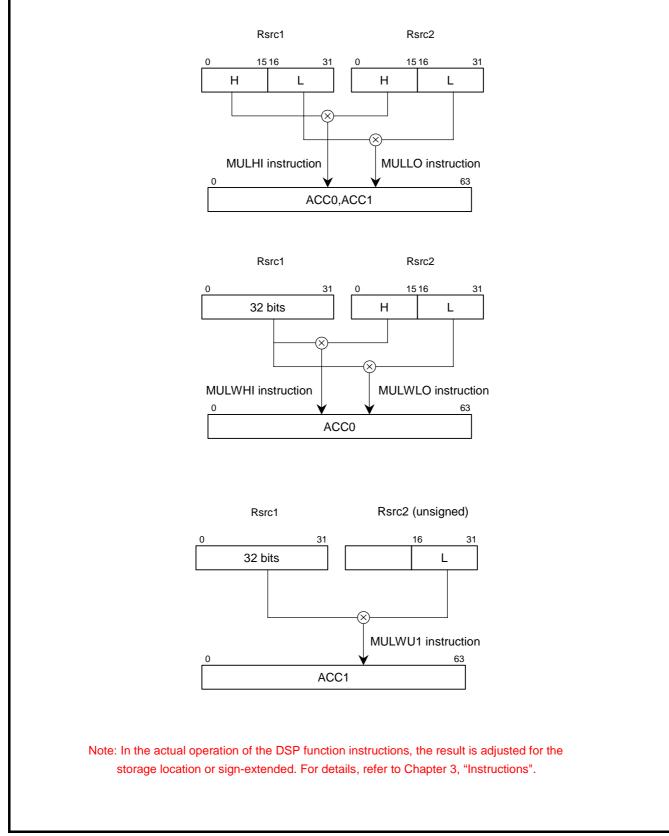

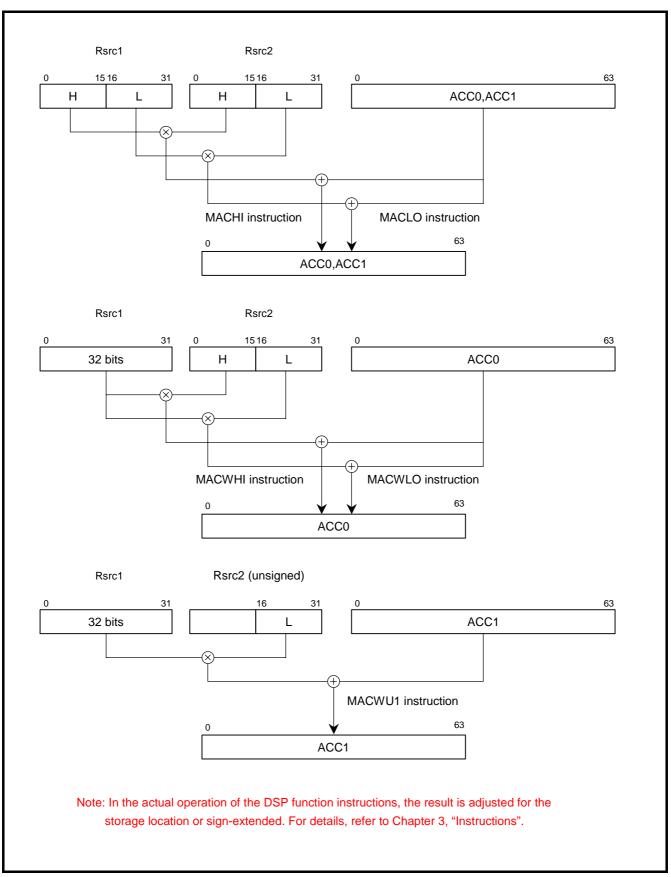

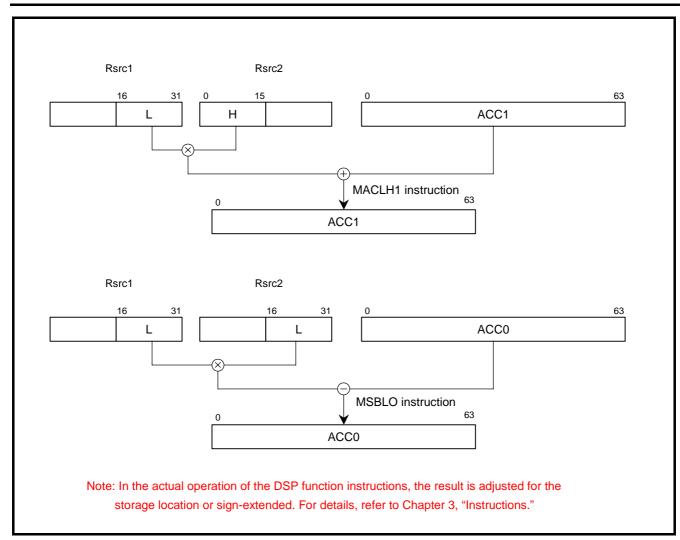

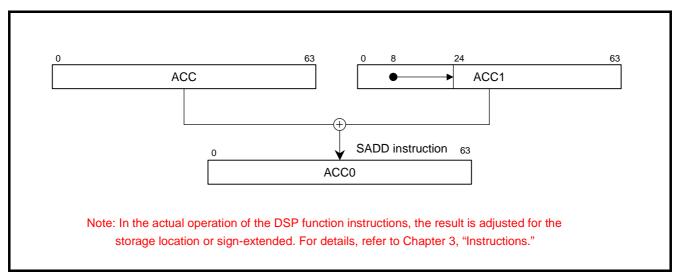

Operation of these instructions are schematically shown in the next pages.

Figure 2.2.2 Operation of the DSP Function Instructions 1 (Multiplication)

### INSTRUCTION SET

2.2 Instruction Set

Figure 2.2.3 Operation of the DSP Function Instructions 2 (Multiply-Accumulate Operation)

Figure 2.2.4 Operation of the DSP Function Instructions 3 (Multiply-Accumulate Operation)

Figure 2.2.5 Operation of the DSP Function Instructions 4 (Addition)

2.2 Instruction Set

Figure 2.2.6 Operation of the DSP Function Instructions 5 (Rounding)

Figure 2.2.7 Operation of the DSP Function Instructions 6 (Transfer between Accumulator and Register)

### 2.2.8 Coprocessor Support Instructions (3 instructions)

These instructions are used for interfacing with a coprocessor, as shown below.

- \* MVTCP Move to Coprocessor register

- \* MVFCP Move from Coprocessor register

- \* OPECP Operate Coprocessor

# 2.3 List of OPSP Extended Instruction Set

The instruction set of the OPSP-CPU has 27 new instructions that have been added as extensions from the M32R family instruction set and 21 conventional instructions which have had their functionality extended.

### 2.3.1 New Extended Instructions of the OPSP-CPU

| Classification        | Mnemonic | Functional outline                                                                       |

|-----------------------|----------|------------------------------------------------------------------------------------------|

| Comparison            | CMPEQ    | Compare between registers                                                                |

| instructions          | CMPZ     | Compare register and immediate 0                                                         |

|                       | PCMPBZ   | Compare register and immediate 0 bytewise                                                |

| Multiplication/       | DIVB     | Divide 8-bit signed integer                                                              |

| division instructions | DIVH     | Divide 16-bit signed integer                                                             |

|                       | DIVUB    | Divide 8-bit unsigned integer                                                            |

|                       | DIVUH    | Divide 16-bit unsigned integer                                                           |

|                       | REMB     | Remainder of 8-bit signed integer                                                        |

|                       | REMH     | Remainder of 16-bit signed integer                                                       |

|                       | REMUB    | Remainder of 8-bit unsigned integer                                                      |

|                       | REMUH    | Remainder of 16-bit unsigned integer                                                     |

| Branch instructions   | BCL      | Branch if condition bit (C) = 1 and store return address in R14                          |

|                       | BNCL     | Branch if condition bit (C) = 0 and store return address in R14                          |

|                       | JC       | Branch if condition bit (C) = 1                                                          |

|                       | JNC      | Branch if condition bit (C) = 0                                                          |

|                       | SC       | Skip parallel execution pair if condition bit (C) = 1                                    |

|                       | SNC      | Skip parallel execution pair if condition bit $(C) = 0$                                  |

| DSP function          | MACLH1   | Multiply-accumulate operation (register × register + accumulator A1                      |

| instructions          |          | → accumulator A1)                                                                        |

|                       | MACWU1   | Multiply-accumulate operation (register × register + accumulator A1                      |

|                       |          | $\rightarrow$ accumulator A1)                                                            |

|                       | MSBLO    | Multiply-accumulate operation (accumulator A0 – register $\times$ register $\rightarrow$ |

|                       |          | accumulator A0)                                                                          |

|                       | MULWU1   | Multiplication (register $\times$ register $\rightarrow$ accumulator A1)                 |

|                       | SADD     | Addition (accumulator A0 + accumulator A1 $\rightarrow$ accumulator A0)                  |

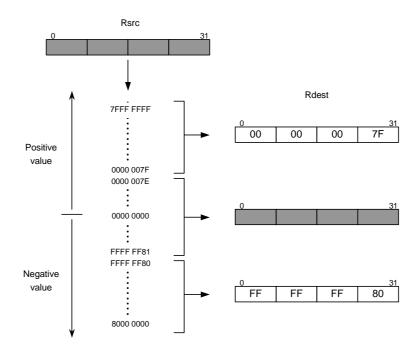

|                       | SATB     | Round register data to byte size                                                         |

|                       | SATH     | Round register data to halfword size                                                     |

| Coprocessor           | MVTCP    | Move to coprocessor register                                                             |

| support instructions  | MVFCP    | Move from coprocessor register                                                           |

|                       | OPECP    | Coprocessor operation                                                                    |

Note: In the table, the accumulators ACC0 and ACC1 are mnemonically expressed as A0 and A1, respectively.

### 2.3.2 Function-Extended Instructions of the OPSP-CPU

| Classification     | Mnemonic | Function-extended content                                             |

|--------------------|----------|-----------------------------------------------------------------------|

| DSP function       | MACHI    | Accumulator A0 or A1 can be specified in the operand                  |

| instructions       | MACLO    | description.                                                          |

|                    | MULHI    |                                                                       |

|                    | MULLO    |                                                                       |

|                    | MVFACHI  |                                                                       |

|                    | MVFACLO  |                                                                       |

|                    | MVFACMI  |                                                                       |

|                    | MVTACHI  |                                                                       |

|                    | MVTACLO  |                                                                       |

|                    | RAC      | Accumulator A0 or A1 can be specified in the operand                  |

|                    | RACH     | description. In addition, the result deriving after left-shifting the |

|                    |          | accumulator bit specified by an immediate (imm1) is rounded.          |

| Arithmetic/logical | SLL      | The parallel-executed instruction category has been changed           |

| instructions       | SLLI     | from the left-side instruction (O-) to the both-side instruction      |

|                    | SRA      | (OS). (For details about the instruction category, refer to Section   |

|                    | SRAI     | 2.5.3, "16-Bit Instruction List by Category."                         |

|                    | SRL      |                                                                       |

|                    | SRLI     |                                                                       |

| Load/store         | STB      | Register update has been added to addressing modes.                   |

| instructions       | STH      |                                                                       |

| EIT related        | TRAP     | The run-time BPC value has been changed from BPC = PC + 4             |

| instructions       |          | to BPC = PC of the next instruction.                                  |

|                    | RTE      | Return to the halfword boundary is possible.                          |

Table2.3.2 List of function-extended instructions

Note: In the table, the accumulators ACC0 and ACC1 are mnemonically expressed as A0 and A1, respectively.

# 2.4 Instruction Formats

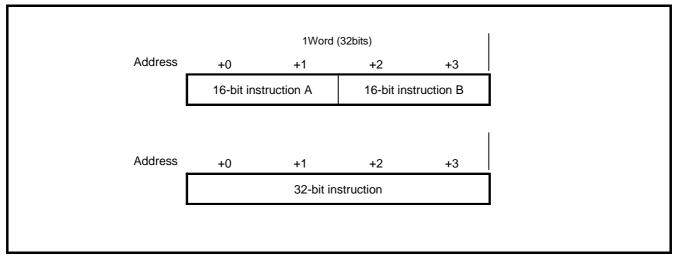

The OPSP-CPU has two instruction formats: a 16-bit instruction, two of which are stored in pairs within the 32-bit word boundary, and a 32-bit instruction. (See Figure 2.4.1.)

The basic instruction formats of the OPSP-CPU are shown in Figure 2.4.2.

Figure 2.4.1 16-Bit and 32-Bit Instructions

| nstruct        | ion forr             | nat>        |          |   | <operation instruction="" of="" the=""></operation> | Frample                       | e instruction>                          |

|----------------|----------------------|-------------|----------|---|-----------------------------------------------------|-------------------------------|-----------------------------------------|

| op1            | R1                   | op2         | R2       | ] | R1 = R1  op  R2                                     | AND                           | Rdest , Rsrc                            |

| op1            | R1                   | C           | ;        | ] | R1 = R1 op c                                        | ADD                           | Rdest , #imm8                           |

| op1            | cond                 | C           | ;        | ] | Branch ( Short Displacement)                        | BC                            | pcdisp8                                 |

|                |                      |             |          |   |                                                     |                               |                                         |

|                | istructio            |             |          |   | Operation of the instruction                        | French                        | instruction                             |

|                | istructio            |             | R2       | с | <operation instruction="" of="" the=""></operation> | <example<br>SRL3</example<br> | e instruction><br>Rdest,Rsrc,#imm1      |

| nstruct<br>op1 | ion forr             | nat><br>op2 | R2<br>R2 | с | R1 = R2 op c                                        | SRL3                          | Rdest , Rsrc , #imm1                    |

| op1            | ion forr<br>R1<br>R1 | nat>        |          | c | R1 = R2 op c<br>Compare and Branch                  | SRL3<br>BEQ                   | Rdest , Rsrc , #imm1<br>Rsrc1 , Rsrc2 , |

| nstruct<br>op1 | ion forr<br>R1       | nat><br>op2 |          | I | R1 = R2 op c                                        | SRL3                          | Rdest , Rsrc , #imm1                    |

Figure 2.4.2 Basic Instruction Formats

# 2.5 Parallel Instruction Execution

### 2.5.1 Instruction Formats

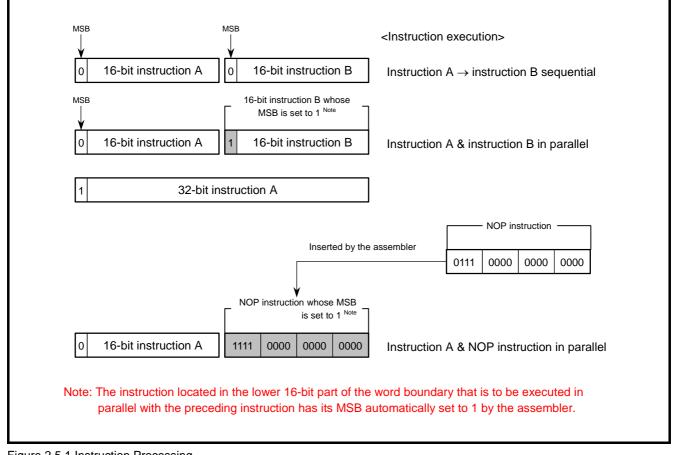

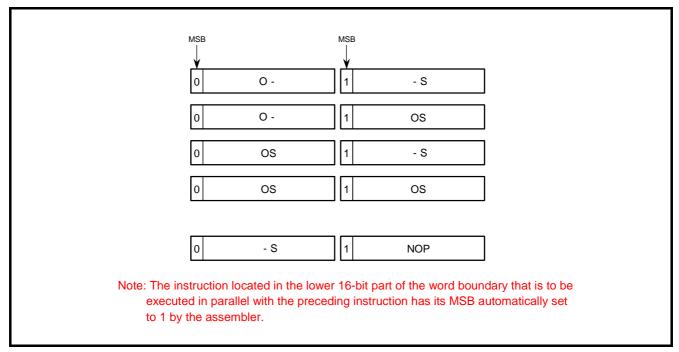

The OPSP-CPU instruction set architecture supports parallel instruction execution for two 16-bit instructions that are stored in pairs within the word boundary. Whether two instructions are executed in parallel is determined by the value of the most significant bit (MSB) of each 16-bit instruction. (The MSB of each instruction only determines the method of instruction execution and does not affect the functionality of the instruction.)

The MSB of any 16-bit instruction that exists in the upper halfword location is always 0. If the MSB of the instruction that follows is also 0, then the two instructions are executed sequentially; if the MSB = 1, the two instructions are executed in parallel.

If the MSB of instruction B in Figure2.5.2 is 0, then instruction A and instruction B are executed sequentially. If the MSB of instruction B is 1, then instruction A and instruction B are executed in parallel. If instruction B needs to be executed in parallel, it is automatically altered to an instruction whose MSB is set to 1 by the assembler. For the same reason, NOP instructions used to adjust the word alignment have always their MSB set to 1 by the assembler.

The MSB of all 32-bit instructions is always 1, so that they are not executed in parallel.

Figure 2.5.1 Instruction Processing

#### 2.5.2 Parallel Instruction Execution in the OPSP

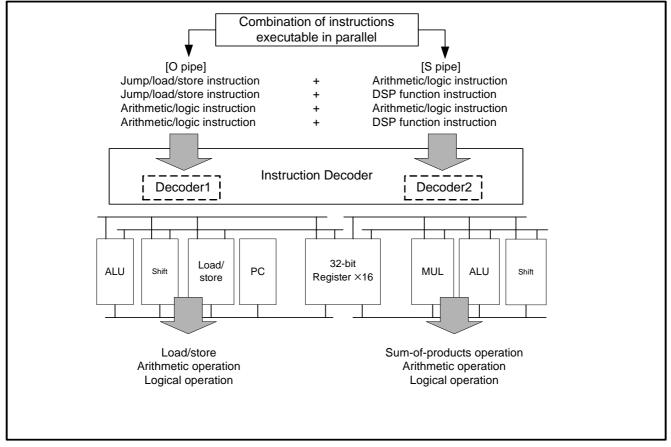

The OPSP-CPU has two pipelines: O pipe and S pipe. Two 16-bit instructions are executed in parallel using these two pipelines.

The 16-bit instructions executed in the S pipe include DSP function instructions and multiplication, arithmetic operation, logical operation, shift, comparison, transfer and NOP instructions. In the O pipe, on the other hand, all 16-bit instructions except DSP function and multiplication instructions can be executed.

Note that 32-bit instructions are not executed in parallel, and that all of them are executed in the O pipe.

Figure 2.5.2 Parallel Instruction Execution Mechanism of the OPSP-CPU

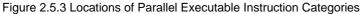

#### 2.5.3 16-Bit Instruction List by Category

The 16-bit instructions that can be executed in parallel are classified into three categories by the executable pipeline.

- Instructions that can be executed in only the O pipe (left-side instruction: O–)

- Instructions that can be executed in only the S pipe (right-side instruction: -S)

- Instructions that can be executed in both O and S pipes (both-side instruction: OS)

The 16-bit instructions classified by category are listed in Table2.5.1.

| O- (left-side instructions) | OS (both-side instructions) | -S (right-side instructions) |

|-----------------------------|-----------------------------|------------------------------|

| BC                          | ADD                         | МАСНІ                        |

| BCL                         | ADDI                        | MACLH1                       |

| BL                          | ADDV                        | MACLO                        |

| BNC                         | ADDX                        | MACWHI                       |

| BNCL                        | AND                         | MACQLO                       |

| BRA                         | СМР                         | MACWU1                       |

| BTST                        | CMPEQ                       | MSBLO                        |

| CLRPSW                      | CMPU                        | MUL                          |

| JC                          | CMPZ                        | MULHI                        |

| JL                          | LDI                         | MULLO                        |

| JMP                         | MV                          | MULWHI                       |

| JNC                         | NEG                         | NULWLO                       |

| LD                          | NOP                         | NULWU1                       |

| LDB                         | NOT                         | MVFACHI                      |

| LDH                         | OR                          | MVFACLO                      |

| LDUB                        | PCMPBZ                      | MVFACMI                      |

| LDUH                        | SLL                         | MVTACHI                      |

| LOCK                        | SLLI                        | MVTACLO                      |

| MVFC                        | SRA                         | RAC                          |

| MVTC                        | SRAI                        | RACH                         |

| RTE                         | SRL                         | SADD                         |

| SETPSW                      | SRLI                        |                              |

| SC                          | SUB                         |                              |

| SNC                         | SUBV                        |                              |

| ST                          | SUBX                        |                              |

| STB                         | XOR                         |                              |

| STH                         |                             |                              |

| TRAP                        |                             |                              |

| UNLOCK                      |                             |                              |

#### Table2.5.1 16-Bit Instruction List by Category

#### 2.5.4 Positions of Parallel Executed Instructions

The 16-bit instruction pairs that can be executed in parallel are limited to the following four combinations of instruction categories.

- Left-side instruction and right-side instruction (O- and -S)

- Left-side instruction and both-side instruction (O- and OS)

- Both-side instruction and right-side instruction (OS and –S)

- Both-side instruction and both-side instruction (OS and OS)

The locations of instruction categories when 16-bit instruction pairs are executed in parallel are shown below.

- Left-side instruction (O–) located in the upper 16-bit part and the right-side instruction (–S) located in the lower 16-bit part

- Left-side instruction (O–) located in the upper 16-bit part and the both-side instruction (OS) located in the lower 16-bit part

- Both-side instruction (OS) located in the upper 16-bit part and the right-side instruction (–S) located in the lower 16-bit part

- Both-side instruction (OS) located in the upper 16-bit part and the other both-side instruction located in the lower 16-bit part

However, if a NOP instruction is located in the lower 16-bit part for the purpose of word alignment, a right-side instruction (–S) may be located in the upper 16-bit part as an instruction pair to be executed in parallel.

#### 2.5.5 Operand Interferences

Two parallel executed 16-bit instructions are executed independently of each other, and not sequenced in time. When executed in parallel, the two instructions are handled as having no mutual dependency with regard to the operand, so that they are not subject to interlock processing. Please be aware of this point when writing a program.

The value of the source operand referenced by a parallel executed instruction pair is one that was stored in the operand immediately before the CPU started executing the instructions in parallel. For example, if in a parallel executed instruction pair, one instruction writes to a register and the other instruction references it, the register value that is referenced is one that was stored in the register immediately before the CPU started executing the instruction pair in parallel. Furthermore, after the instruction pair was executed, the result is written to the register.

Note, however, that if two instructions are executed in parallel that write to the same register (collision of writes to a register), program operation cannot be guaranteed.

#### (1) Examples of operand interferences in general-purpose registers

The following shows typical examples of operand interferences in general-purpose registers attributable to two transfer instructions (MV instructions).

Example 1: MV R1,R0 || MV R2,R1 Example 2: MV R1,R0 || MV R1,R2 Note: the symbol || denotes that two instructions are executed in parallel.

In example 1, one of the two instructions in pairs writes to a register (R1) and the other references it. In this case, R1 is assigned the value of R0. Similarly, R2 is assigned the value of R1 before assignment to R1 (i.e., the value of R1 before the instruction "MV R1,R0" is executed).

Example 2 is an example where two instructions in the instruction pair write to the same register (collision of writes to a register). In this case, the registers accessed for write by two MV instructions both are R1, so that the value of R1 after instruction execution is indeterminate.

#### (2) Examples of operand interferences in control registers

In addition to general-purpose registers, operand interferences will occur in control registers such as the PSW and CBR that include the condition bit (C).

Example 3: When two instructions are executed successively

CMP R1,R0 BC \_label

Example 4: When two instructions are executed in parallel

CMP R1,R0 || BC \_label

Note: the symbol || denotes that two instructions are executed in parallel.

In example 3, the comparison instruction (CMP) is executed before the conditional branch instruction (BC) is executed. In this case, the condition bit (C) is updated as a result of the CMP instruction executed, and the BC instruction references this updated condition bit (C) to determine whether or not to branch.

In example 4, the CMP and the BC instructions are executed in parallel. The BC instruction references the condition bit (C) before the CMP instruction is executed, to determine whether or not to branch. Be aware that the condition bit (C) is referenced before it is operated on by execution of the CMP instruction. The result of the CMP instruction executed is reflected in the condition bit (C) after parallel instruction execution.

Furthermore, if two instructions are executed in parallel that will change the condition bit (C), the value of the condition bit (C) after instruction execution becomes indeterminate as in the case of a collision of writes to a register that occurs in general-purpose registers. Shown below are examples where the condition bit (C) becomes indeterminate after an instruction pair is executed in parallel.

| Example 5:CMP                                                                                                                      | R1,R2  | ll | ADDX | R3,R4 |  |

|------------------------------------------------------------------------------------------------------------------------------------|--------|----|------|-------|--|

| Example 6: MVTC                                                                                                                    | R1,PSW | II | ADDX | R1,R2 |  |

| Example 7: TRAP                                                                                                                    | #1     |    | CMP  | R3,R4 |  |

| Example 8: RTE                ADDX       R3,R4         Note: the symbol    denotes that two instructions are executed in parallel. |        |    |      |       |  |

This page is blank for reasons of layout.

## CHAPTER 3 INSTRUCTIONS

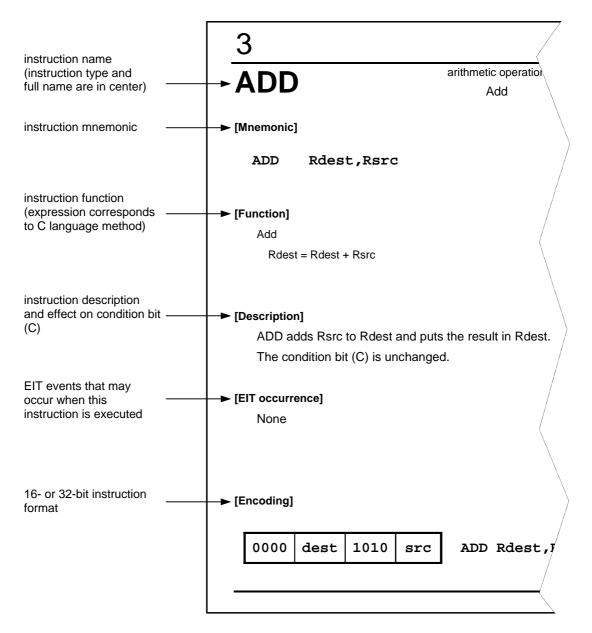

## 3.1 Guide to Detailed Instruction Description

The following outlines each item that is described in the detailed description of instructions in the pages to follow.

#### [Mnemonic]

The mnemonics of the OPSP-CPU consist of an instruction and the operand description that follows. The operand is the target to be operated on by the instruction.

| Operand<br>description <sup>Note</sup> | Addressing mode            | Target to be operated on by instruction                                 |

|----------------------------------------|----------------------------|-------------------------------------------------------------------------|

| R                                      | Register direct            | General-purpose register of the OPSP-CPU (R0-R15)                       |

| CR                                     | Control register           | Control register of the OPSP-CPU                                        |

|                                        |                            | (CR0=PSW, CR1=CBR, CR2=SPI, CR3=SPU, CR5=EVB, CR6=BPC)                  |

| CPR                                    | Coprocessor register       | Register of the coprocessor connected to the OPSP-CPU                   |

| А                                      | Accumulator                | Content of the OPSP-CPU accumulator (A0, A1)                            |

| @Rn                                    | Register indirect          | Memory content whose address is indicated by a register value           |

| @(disp, Rn)                            | Register relative indirect | Memory content whose address is indicated by (register value) + (16-bit |

|                                        |                            | constant that is sign-extended to 32 bits)                              |

| @Rn+                                   | Register indirect +        | Register value incremented by 4, 2, or 1 (Memory content whose          |

|                                        | register update            | address is indicated by a preupdate register value)                     |

| @+Rn                                   | Register indirect +        | Register value incremented by 4 (Memory content whose address is        |

|                                        | register update            | indicated by an updated register value)                                 |

| @ - Rn                                 | Register indirect +        | Register value decremented by 4 (Memory content whose address is        |

|                                        | register update            | indicated by an updated register value)                                 |

| #imm                                   | Immediate                  | Immediate value (For details on how the value is handled, refer to the  |

|                                        |                            | detailed description of each instruction.)                              |

| pcdisp                                 | PC relative                | Memory content whose address is indicated by (PC value) + (8, 16, or    |

|                                        |                            | 24-bit displacement which is sign-extended to 32 bits and then shifted  |

|                                        |                            | left 2 bits).                                                           |

Table 3.1.1 List of Operand description

Note: In operand descriptions "Rsrc" and "Rdest," src and dest each represent a general-purpose register number (0–15). In operand descriptions "CRsrc" and "CRdest," src and dest each represent a control register number (0–3, 5, or 6). In operand descriptions "Asrc" and "Adest," src and dest each represent an accumulator number (0 or 1).

#### [Function]

Operation of each instruction is described by first outlining what the instruction does and then showing a C language based description of the operation. The description of instruction operation is outlined below.

| Operator                                                                                   | Operation performed                                                                        |  |

|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|

| +                                                                                          | Addition (binary operator)                                                                 |  |

| -                                                                                          | Subtraction (binary operator)                                                              |  |

| *                                                                                          | Multiplication (binary operator)                                                           |  |

| /                                                                                          | Division (binary operator)                                                                 |  |

| %                                                                                          | Remainder calculation (binary operator)                                                    |  |

| ++                                                                                         | Increment (unary operator)                                                                 |  |

|                                                                                            | Decrement (unary operator)                                                                 |  |

| -                                                                                          | Sign inversion (unary operator)                                                            |  |

| =                                                                                          | Assign right side to left side (assignment operator)                                       |  |

| +=                                                                                         | Add left and right side variables and assign the result to left side (assignment operator) |  |

| -= Subtract right side variable from left side variable and assign the result to left side |                                                                                            |  |

|                                                                                            | (assignment operator)                                                                      |  |

| >                                                                                          | Greater than (relational operator)                                                         |  |

| <                                                                                          | Smaller than (relational operator)                                                         |  |

| >=                                                                                         | Greater than or equal (relational operator)                                                |  |

| <=                                                                                         | Smaller than or equal (relational operator)                                                |  |

| ==                                                                                         | Equal (relational operator)                                                                |  |

| !=                                                                                         | Not equal (relational operator)                                                            |  |

| &&                                                                                         | AND (logical operator)                                                                     |  |

| Ш                                                                                          | OR (logical operator)                                                                      |  |

|                                                                                            | NOT (logical operator)                                                                     |  |

| ?:                                                                                         | Create conditional expression (conditional operator)                                       |  |

#### Table 3.1.3 Description of Operations (Bitwise Operators)

| Operator | Operation performed         |  |

|----------|-----------------------------|--|

| <<       | Shift the bit left          |  |

| >>       | Shift the bit right         |  |

| &        | Bitwise AND                 |  |

|          | Bitwise OR                  |  |

| ٨        | Bitwise exclusive-OR (EXOR) |  |

| ~        | Bit inversion               |  |

#### Table 3.1.4 Data Types

| Representation | Туре    | Signed or unsigned | Bit length | Range of values                  |

|----------------|---------|--------------------|------------|----------------------------------|

| char           | Integer | Signed             | 8          | -128 to +127                     |

| short          | Integer | Signed             | 16         | -32,768 to +32,767               |

| int            | Integer | Signed             | 32         | -2,147,483,648 to +2,147,483,647 |

| unsigned char  | Integer | Unsigned           | 8          | 0 to 255                         |

| unsigned short | Integer | Unsigned           | 16         | 0 to 655,535                     |

| unsigned int   | Integer | Unsigned           | 32         | 0 to 4,294,967,295               |

| signed64bit    | Integer | Signed             | 64         | Signed 64-bit integer            |

|                |         |                    |            | (when operating on accumulators) |

#### [Description]

The function of each instruction is detailed here. Furthermore, changes of the condition bit (C) in the PSW register that occur as a result of execution of the instruction are described.

#### [EIT occurrence]

A generated EIT means an EIT event (exception, interrupt, or trap) that may occur as a result of execution of the instruction. The EIT events that are likely to occur as a result of instruction execution include an address exception, trap and a privileged instruction exception.

#### [Encoding]

A 16-bit or 32-bit instruction bit pattern is shown. In the instruction format, src and dest each represent the corresponding register number, while imm and disp represent immediate and displacement values, respectively. (The magnitude of the numeric value that is assigned to each bit field is determined by the field width.) For details about the instruction format, refer to Section 2.3, "Instruction Formats," in Chapter 2.

## 3.2 Detailed Description of Instructions

Each instruction of the OPSP-CPU is described in detail beginning with the next page. Instructions are listed in alphabetical order. Note that each page consists of the items described below.

## ADD

arithmetic operation instruction Add

## [Mnemonic]

ADD Rdest,Rsrc

## [Function]

Add

Rdest = Rdest + Rsrc

### [Description]

ADD adds Rsrc to Rdest and puts the result in Rdest. The condition bit (C) dose not changed.

#### [EIT occurrence]

None

## [Encoding]

0000 dest 1010 src

ADD Rdest,Rsrc

## ADD3

arithmetic operation instruction Add 3-operand

## ADD3

### [Mnemonic]

ADD3 Rdest,Rsrc,#imm16

### [Function]

Add

Rdest = Rsrc + ( signed short ) imm16;

#### [Description]

ADD3 adds the 16-bit immediate value to Rsrc and puts the result in Rdest. The immediate value is sign-extended to 32 bits before the operation.

The condition bit (C) dose not changed.

#### [EIT occurrence]

None

#### [Encoding]

1000 dest 1010

src

imm16

ADD3 Rdest,Rsrc,#imm16

## ADDI

arithmetic operation instruction Add immediate

#### [Mnemonic]

ADDI Rdest,#imm8

#### [Function]

Add

Rdest = Rdest + ( signed char ) imm8;

#### [Description]

ADDI adds the 8-bit immediate value to Rdest and puts the result in Rdest. The immediate value is sign-extended to 32 bits before the operation.

The condition bit (C) dose not changed.

#### [EIT occurrence]

None

## [Encoding]

0100 dest imm8

ADDI Rdest,#imm8

## ADDV

arithmetic operation instruction Add with overflow checking

## ADDV

## [Mnemonic]

ADDV Rdest,Rsrc

## [Function]

Add

$\label{eq:Rdest} \begin{aligned} Rdest = ( \ signed \ ) \ Rdest + ( \ signed \ ) \ Rsrc; \\ C = overflow \ ? \ 1 \ : 0 \end{aligned}$

## [Description]

ADDV adds Rsrc to Rdest and puts the result in Rdest. The condition bit (C) is set when the addition results in overflow; otherwise it is cleared.

src

#### [EIT occurrence]

None

## [Encoding]

0000 dest 1000

ADDV Rdest,Rsrc

## ADDV3

arithmetic operation instruction Add 3-operand with overflow checking

## ADDV3

## [Mnemonic]

ADDV3 Rdest,Rsrc,#imm16

## [Function]

#### Add

Rdest = ( signed ) Rsrc+ ( signed )( (signed short)imm16); C = overflow ? 1 : 0

## [Description]

ADDV3 adds the 16-bit immediate value to Rsrc and puts the result in Rdest. The immediate value is sign-extended to 32 bits before it is added to Rsrc.

The condition bit (C) is set when the addition results in overflow; otherwise it is cleared.

#### [EIT occurrence]

None

#### [Encoding]

1000 dest 1000 src imm16

ADDV3 Rdest,Rsrc,#imm16

## ADDX

arithmetic operation instruction Add with carry

## ADDX

## [Mnemonic]

ADDX Rdest,Rsrc

## [Function]

#### Add

$\label{eq:Rdest} \begin{aligned} Rdest = (\ unsigned \ ) \ Rdest + (\ unsigned \ ) \ Rsrc + C; \\ C = carry_out \ ? \ 1 : 0; \end{aligned}$

## [Description]

ADDX adds Rsrc and C to Rdest, and puts the result in Rdest. The condition bit (C) is set when the addition result cannot be represented by a 32-bit unsigned integer; otherwise it is cleared.

#### [EIT occurrence]

None

## [Encoding]

0000 dest 1001 src

ADDX Rdest,Rsrc

## AND

logic operation instruction AND

## [Mnemonic]

AND Rdest,Rsrc

## [Function]

Logical AND

Rdest = Rdest & Rsrc;

## [Description]